# 50Msps 12-Bit SAR ADC IP Marketing Brief

### **Epoch Microelectronics, Inc.** Valhalla, NY

© Epoch Microelectronics, Inc. 420 Columbus Avenue, Suite 204, Valhalla, NY 10595

## 12-Bit 50Msps SAR ADC: Features/Deliverables

#### Features:

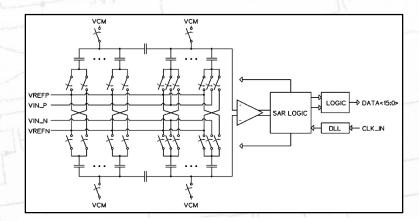

- Non-binary switch capacitor SAR ADC architecture that relaxes voltage reference settling requirements

- Incorporates calibration logic to calibrate linearity of SAR ADC

- Includes delay lock loop for internal high speed clock generation

#### **Deliverables:**

- White Box:

- Cadence library including schematics, layout, and test benches

- GDS2, CDL netlist, DRC/LVS/ERC reports

- Verilog and .LIB files

- Evaluation report

- Black Box:

- GDS2, CDL netlist, DRC/LVS/ERC reports

- Verilog and .LIB files

- Encrypted SPICE netlist

- Evaluation report

### **12-Bit 50Msps Switch Capacitor SAR ADC**

| Technology             | Global Foundries<br>40nm CMOS       |  |  |  |

|------------------------|-------------------------------------|--|--|--|

| Process Options        | 6L1x_1T6x_1T18x_LB                  |  |  |  |

| Analog Supply Voltage  | 1.1V/1.8V                           |  |  |  |

| Digital Supply Voltage | 1.1V                                |  |  |  |

| Sampling Rate          | 50Msps                              |  |  |  |

| Input Voltage Swing    | 2.2V <sub>ppd</sub>                 |  |  |  |

| ENOB                   | 9.4bit (10.2 @40Msps)               |  |  |  |

| SNDR                   | 58.1dB (63dB @40Msps)               |  |  |  |

| Active Chip Area       | 0.15mm <sup>2</sup>                 |  |  |  |

| Power (Analog)         | 4.1mW                               |  |  |  |

| Power (Digital)        | 6.1mW                               |  |  |  |

| Status                 | Respin needed – See<br>Errata Slide |  |  |  |

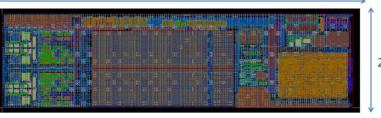

750um

200um

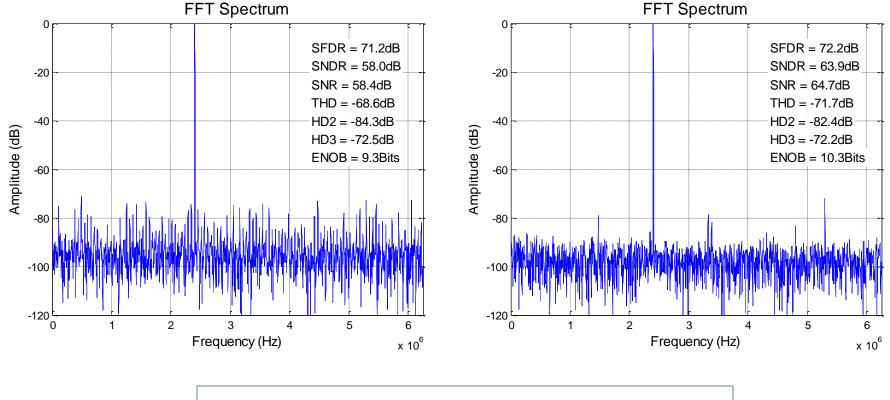

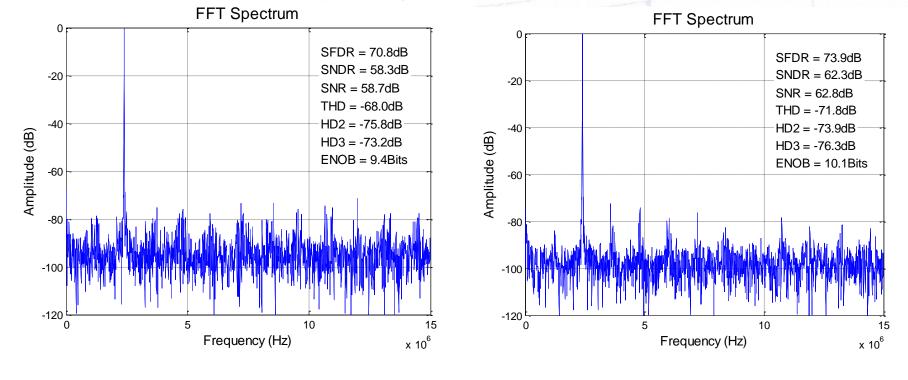

### Measured Spectrum: TT Sample @ 12.5Msps

#### **Uncalibrated ADC**

#### Calibrated/adjusted ADC

ENOB = 9.3 (uncalibrated) / 10.3 (calibrated)

### Measured Spectrum: TT Sample @ 20Msps

#### **Uncalibrated ADC**

#### Calibrated/adjusted ADC

ENOB = 9.3 (uncalibrated) / 10.1 (calibrated)

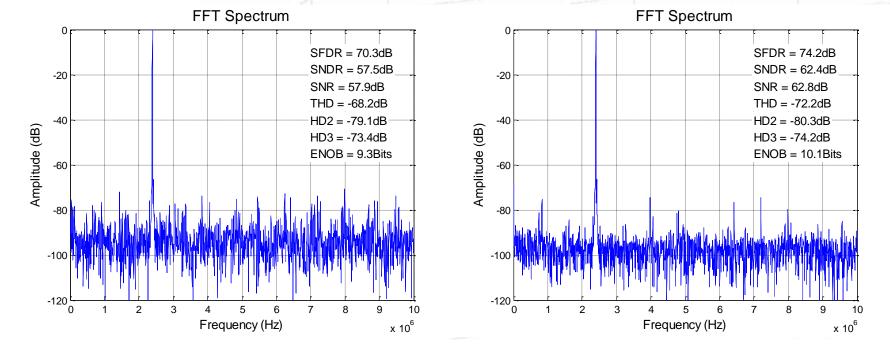

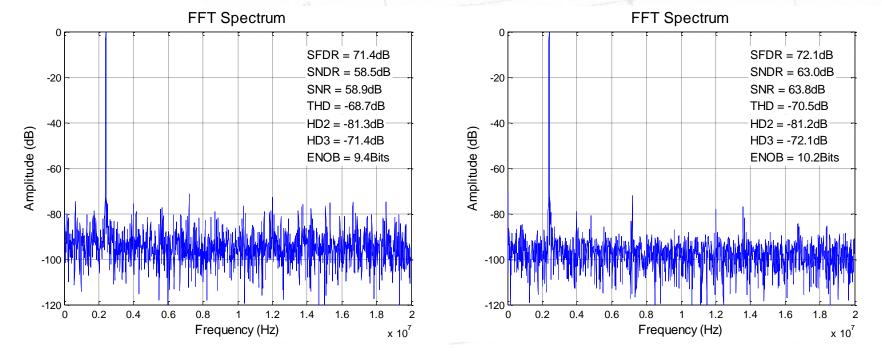

### Measured Spectrum: TT Sample @ 30Msps

#### **Uncalibrated ADC**

#### Calibrated/adjusted ADC

ENOB = 9.4 (uncalibrated) / 10.1 (calibrated)

### Measured Spectrum: TT Sample @ 40Msps

#### **Uncalibrated ADC**

#### Calibrated/adjusted ADC

ENOB = 9.4 (uncalibrated) / 10.2 (calibrated)

### Measured Spectrum: TT Sample @ 50Msps

#### **Uncalibrated ADC**

#### Calibrated/adjusted ADC

ENOB = 9.0 (uncalibrated) / 9.4 (calibrated)

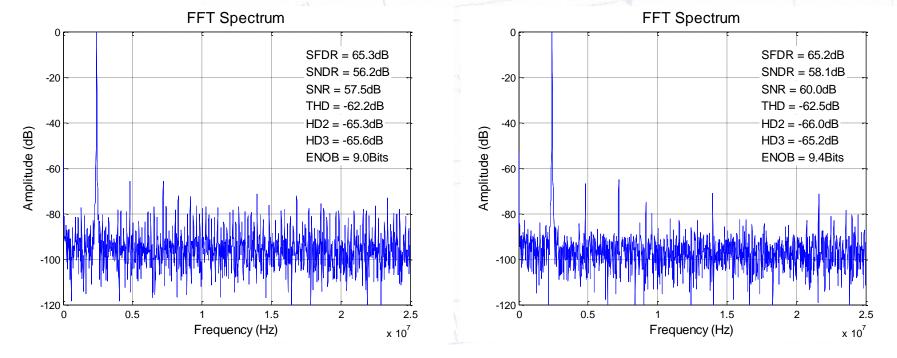

### Measured ENOB vs Sampling Frequency

| Fsample (MHz)       | 12.5 | 20   | 30   | 40   | 50  |

|---------------------|------|------|------|------|-----|

| Uncalibrated        | 9.3  | 9.3  | 9.4  | 9.4  | 9.0 |

| Calibrated/Adjusted | 10.3 | 10.1 | 10.1 | 10.2 | 9.4 |

[Unit: Bits]

Measurement shows degradation at 50Msps

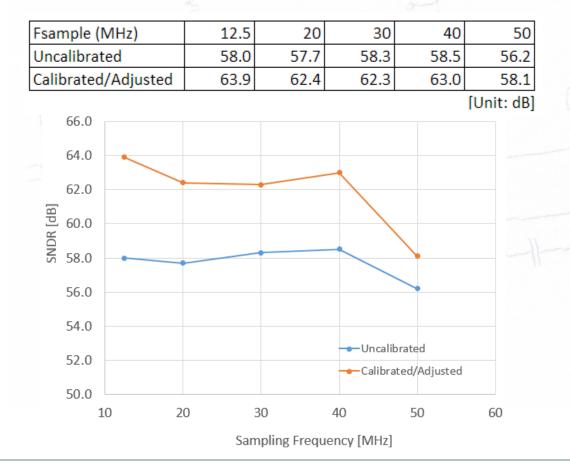

### Measured SNDR vs Sampling Frequency

Measurement shows degradation at 50Msps

### Errata

- (1) ADC calibration logic does not have enough range (i.e. bit length) and MSB correction value saturates to maximum code. Verilog needs to be updated and synthesis/P&R must be repeated to fix this issue.

- (2) DLL DCO reset pulse is too long which results at shorter sampling/conversion cycles not allowing time to settle at 50Msps

## Thank you!

Ken Suyama Email: <u>ken.suyama@epochmicro.com</u> Phone: 914-332-8570x222

© Epoch Microelectronics, Inc. 420 Columbus Avenue, Suite 204, Valhalla, NY 10595